2つのPLLを使ったスプリアス低減と高分解能化

2つのPLLを使ったスプリアス低減と高分解能化

PCK3GF-1

PLLには分周回路のタイプによりINTEGER(整数の分周)タイプとFRACTIONAL(分数の分周)タイプの2つの方式があります。FRACTIONALの場合、 例えば、分母が256であれば10MHzの位相比較周波数で=39.0625KHzとなり位相比較周波数は10MHzのまま細かい分周比が得られる利点があります。位相比較周波数が高いと ループゲインが大きくできるのでクローズループ帯域が広くなり、高分解能でかつ低位相雑音が得られます。このFRACTIONAL PLLですが今までその分母の数値は4096とかで あまり大きなものがありませんでしたが、Hittiteからこの分母が24ビット、即ち2^24という大きな値を持つHMC830LP6という製品が発売されました。

PCK3GF-1 の詳しい仕様は、こちらをご覧ください。

アナログデバイス社の類似PLL ICとの比較

| HMC830LP6 | ADF4350 | |

| 周波数範囲 | 25~3000MHz | 137.5~4400MHz |

| VCO周波数 | 2^24=16777216 | 2^12=4096 |

| 位相比較周波数(Max.) | 100MHz(80MHz) | 32MHz |

| 周波数発生可能分解能 | 2.98Hz at Fpd=50MHz | 7812Hzat Fpd=32MHz |

| Figure of Merit | -227dBm/Hz | -220dBm/Hz |

| Typ.位相雑音 | -110dBc/Hz | -90dBc/Hz |

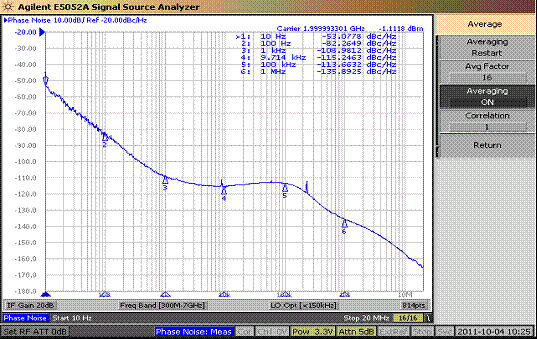

下図はHMC830LP6を2GHz、Pfd=50MHzで動作させたときの位相雑音特性実測値です。

この位相雑音特性はVCO内蔵のPLLとしてはおそらく最高レベルの性能を持っていると思います。 約3Hzステップの半分が周波数誤差になりますので最大誤差1.5Hz程度ですので多くの用途では十分かも知れません。ただしこの周波数誤差が問題になる場合は HCM830ではEXACT FREQモードというがあります。最小ステップの条件と最小ステップの整数倍がFpdという2つの条件を満たす 必要がありますが数10KHzステップ以上ではこの機能を使えは周波数誤差を無くすことは可能です。さらに分解能を上げたい場合ですが、このPLL ICを2個縦続接続すると 1Hz以下でも周波数誤差をなくすことが出来ます。

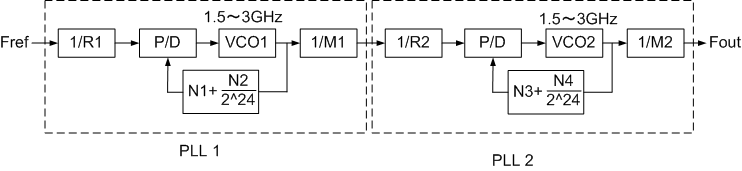

出力周波数は

Fout= Fref *(1/R1)*(N1+N2/2^24)*(1/M1)*(1/R2)* (N3+N4/2^24)*((1/M2)

で決まります。 R1,R2,M1,M2,N1~N4はすべて整数の変数で目的周波数になる組み合わせは多数存在します。問題はこの組み合わせを見つけるのが意外と大変で時間がかかります。 ネスト数は変数の数だけあるので組み合わせをサーチするだけで1ポイントあたり最高速のPCを使っても数分~10分程度かかりました。周波数誤差が完全にゼロにならず ある程度残る周波数もありますがその誤差は10^-7Hzオーダーで十分に小さいレベルまで下げることができます。目的周波数の組み合わせを1つだけ見つければ 本来は良いのですが実際には複数の組み合わせを見つけています。理由はスプリアスを逃す組み合わせを見つけるためです。PLLの特有のスプリアスとして基準信号 或いは位相比較周数の高調波が出力周波数に近づくとPLLのループ帯域内のビート信号として回り込んで厄介なスプリアスとして現われます。ループ帯域を狭めれば 発生頻度は少なくなりますが位相雑音特性を考えるとループ帯域は広いほうが良いわけでそれもできません。複数の組み合わせがあることでスプリスの発生しそうな 設定値は除外してスプリアスを低減できます。周波数1ポイント毎に最良の設定値をあらかじめ計算で求めてメモリーに記憶させておく必要があります。 周波数ポイントが多い場合、即ち周波数分解能を細かくすると大きな容量のEEPROMメモリーが必要になります。このようなコンセプトで2つのPLLを使ったシンセサイザーを 当社で製品化したものがPCK3GF-1です。シールドを厳重にしなくてもスプリアスが低減できコストを押さえて位相雑音を改善させることが可能になりました。

この製品の詳しい仕様は、こちらをご覧ください。