100MHz低位相雑音基準源

100MHz低位相雑音基準源

REF10MF

マイクロ波帯の周波数シンセサイザーで低位相雑音にしようとすると、PLLの位相比較周波数はなるべく高くしたほうが有利です。一方 安定度の良い標準的な基準周波数は5MHzか10MHzが多いため、外部10MHzで同期のかけられる100MHzの低位相雑音基準信号モジュールREF10MFを開発しました。

| 出力周波数 | 100MHz |

| 出力ポート数 | 2ポート |

| 出力レベル | 3.3V CMOS |

| 外部基準信号レベル | -6dBm~+10dBm サイン波または矩形波 |

| 外部基準信号入力インピーダンス | 1kΩ |

| スプリアス | -70dBc 以下 (但し、高調波成分は除く) |

| PLLループ帯域 | 10Hz |

| 外部クロック時ロックレンジ | 1kΩ |

| 外部基準信号入力インピーダンス | 10MHz±25ppm |

| 内部クロック時周波数調整範囲 | 10MHz±25ppm |

| 電源電圧 | +3.3V±5% 最大 100mA |

| 外形寸法 | W25.4 x D20.32 x H7.62(mm) |

| 動作温度範囲 | 0~+60℃ 保存温度範囲 -30~+70℃ |

ループ帯域が10Hzですので電源ラインノイズが外部基準信号に混入しても除去もできます。外部基準は標準で10MHzですがシリアルデータ(SCI又はSPI)で 5MHz等に変更してその設定を記憶させられます。

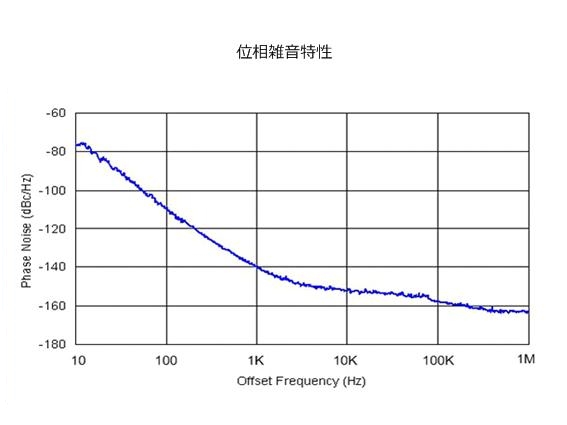

位相雑音特性は最も重要なスペックであり使用しているVCXOの性能によって決まります。今回VCXOはCRYSTEK社製を使用しました。 日本メーカーのものは位相雑音特性がよいものは必ず周波数安定度もよく、結果として高価で採用しませんでした。REF10MFに必要なVCXOは周波数安定度などどうでもよく 位相雑音だけ良ければ良いのですが、そのようなカテゴリーの製品は需要がないのか見つかりません。最近のTCXOやVCXOを分解すると発振回路はIC化されているのがほとんどで、 周波数安定度は振動子と補正回路でよくなりますが、位相雑音をよくするのはIC化された回路による影響が大きいようです。位相雑音は水晶振動子のQ値に依存すると思って いましたが、調べてみるとそう単純ではないようです。試しにQ値の違う振動子を選んで同じ発振器比較しましたが、Q値と位相雑音性能に相関は小さく、むしろ同じ水晶片を 違う発振回路で動作させた方が大きな違いが出ましたので、回路の工夫次第で位相雑音は下げられるようです。おそらくある程度良くなると水晶のQ値の違いが出るのだと思いますが、 水晶発振回路は簡単なようでなかなか奥が深いです。

この製品の詳しい仕様は、こちらをご覧ください。